2025-04-18

Layout

- 이제부터 Layout 최소화를 위해서는 path를 잘 정하는 것이 중요하다.

- 입력 Cont는 계단식으로 하는 것이 최소화에 유리하며, 상향식, 하향식은 달라질 수 있다.

- VOUT은 가능한 오른쪽 Cont인 것이 최소화에 유리하다.

- 직렬 구조의 MOS는 VOUT이 가장 오른쪽인 경로로 정한다. EX) A > B > C

- 경로의 시작점은 VOUT이 가장 우측으로 가게 정한다

CMOS 3NAND

Schematic & Layout

Layout 순서

- nMOS가 직렬 구조 이므로 VOUT이 가장 우측으로 가기 위해서는 C > B > A를 경로로 한다.

- pMOS는 VDD부터 시작하게 한다.

- Schematic에 맞게 배선 연결을 한다.

- 현재 VOUT 배선은 pMOS는 2, 4번 nMOS는 4번 Cont(좌측부터 1)이다. 이 경우 최소화를 위해서는 VINC가 제일 위로 배치하는 것이 유리하다.

- 이를 토대로 Layout 결과 최소 크기는 5.62um이다.

DRC & LVS

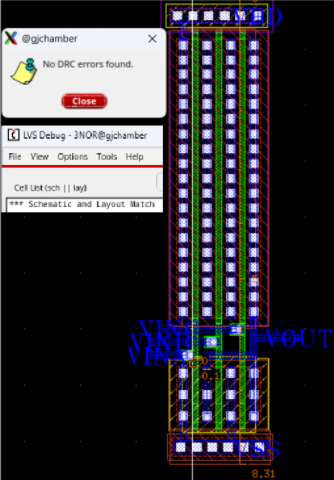

CMOS 3NOR

Schematic & Layout

Layout 순서

- 직렬인 pMOS를 기준으로 경로는 A > B > C로 정한다.

- nMOS는 VSS부터 시작해 위의 경로로 전행한다.

- Schematic에 맞게 배선을 진행한다.

- 최종적으로 8.31um가 나온다.

DRC & LVS

CMOS 4NAND

Schematic & Layout

Layout 순서

- 다른 Layout과 동일하게 진행

DRC & LVS

CMOS 4NOR

Schematic & Layout

Layout 순서

- 다른 Layout과 동일하게 진행

DRC & LVS

728x90

'ARM 코어 기반 반도체 설계 제어 전문가 과정 > CUSTOM IC ONE CHIP' 카테고리의 다른 글

| [CUSTOM IC ONE CHIP] 4X1 MUX - Logic OR Switch (15) (0) | 2025.04.28 |

|---|---|

| [CUSTOM IC ONE CHIP] 2X1 MUX - Logic OR Switch (14) (0) | 2025.04.28 |

| [CUSTOM IC ONE CHIP] Layout (12) (0) | 2025.04.17 |

| [CUSTOM IC ONE CHIP] CMOS Schematic (11) (0) | 2025.04.16 |

| [CUSTOM IC ONE CHIP] Channel Length Modulation (10) (0) | 2025.04.14 |