2025-04-23

MUX

- 입력 신호중 1개를 선택해 출력하는 장치이다.

- 입력 갯수는 2진수로 이를 선택하기 위한 S입력이 존재한다.

- S의 비트수 N, INPUT 갯수 2^N개

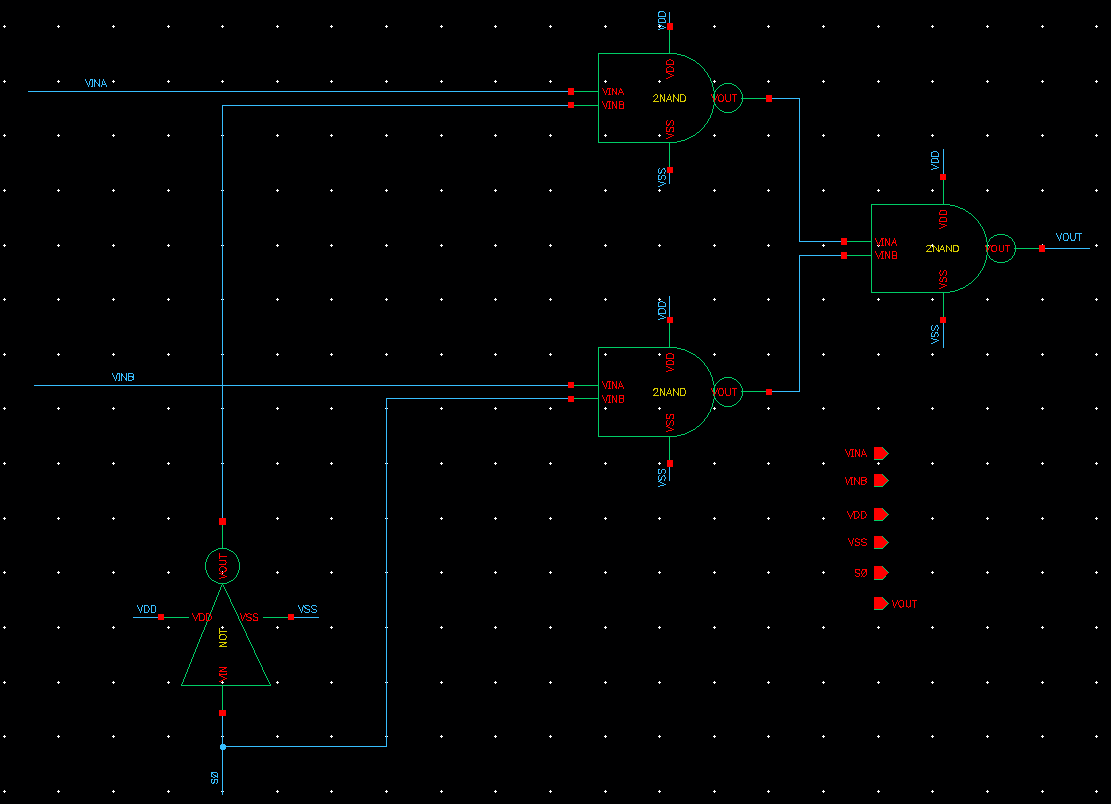

2X1 MUX Logic

Schematic

- 트랜지스터 수 : 4(2NAND) X 3 + 2(NOT) = 14개

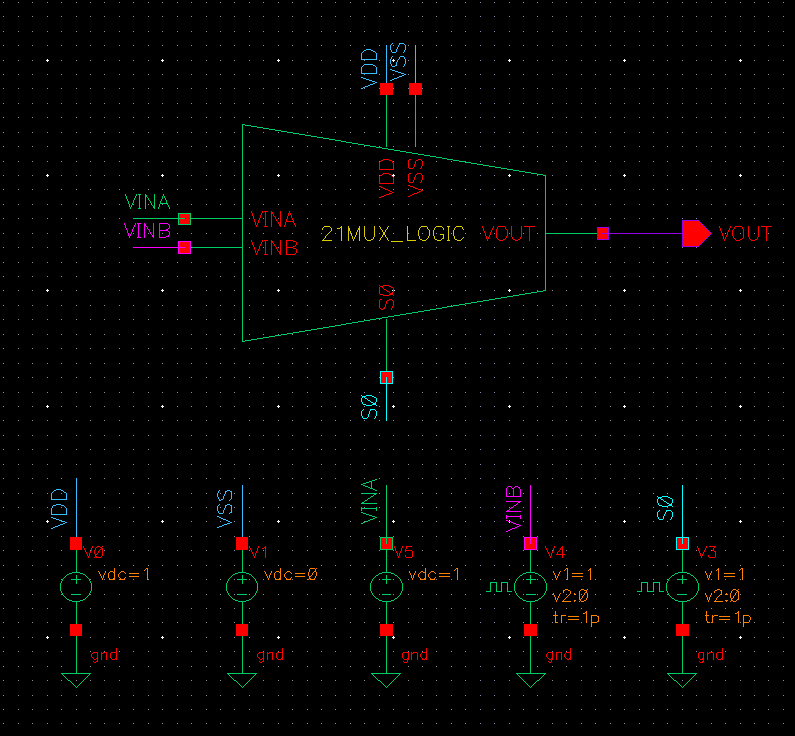

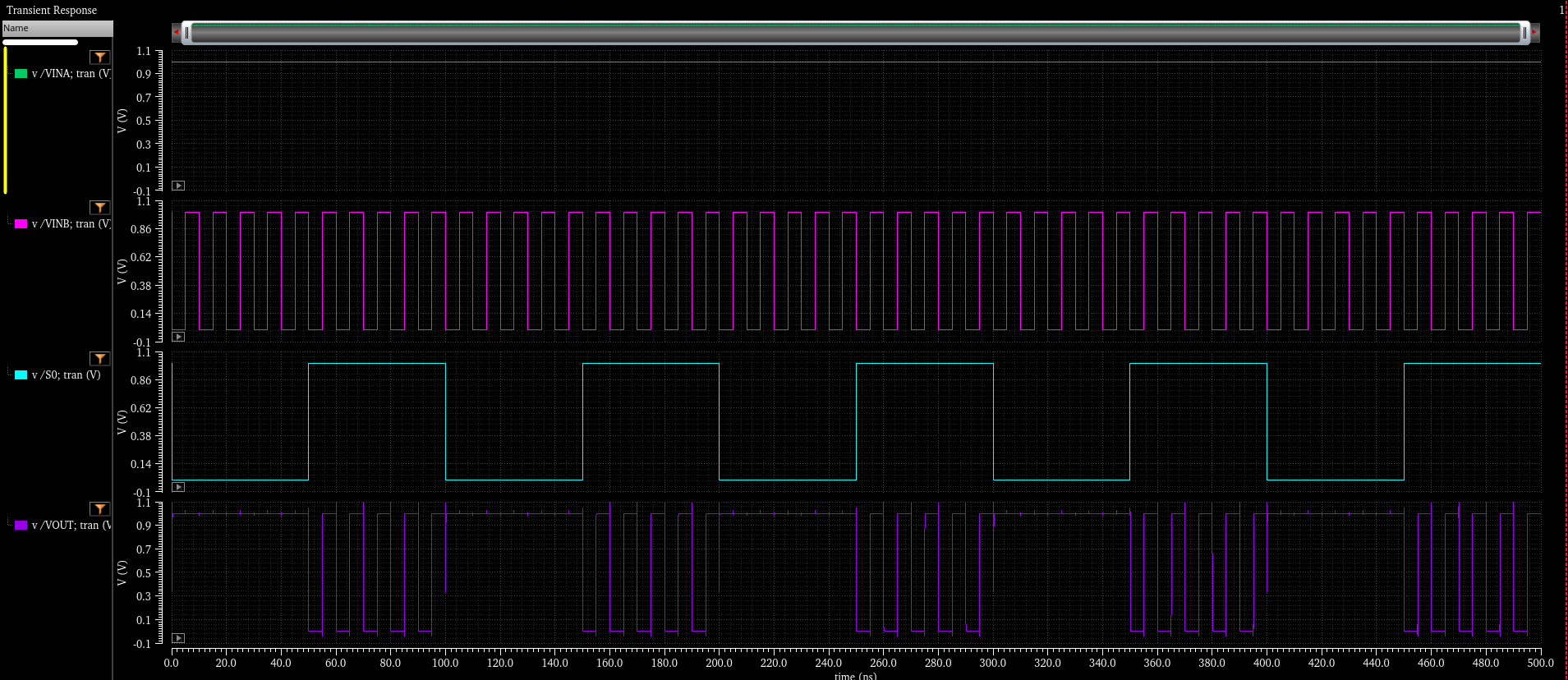

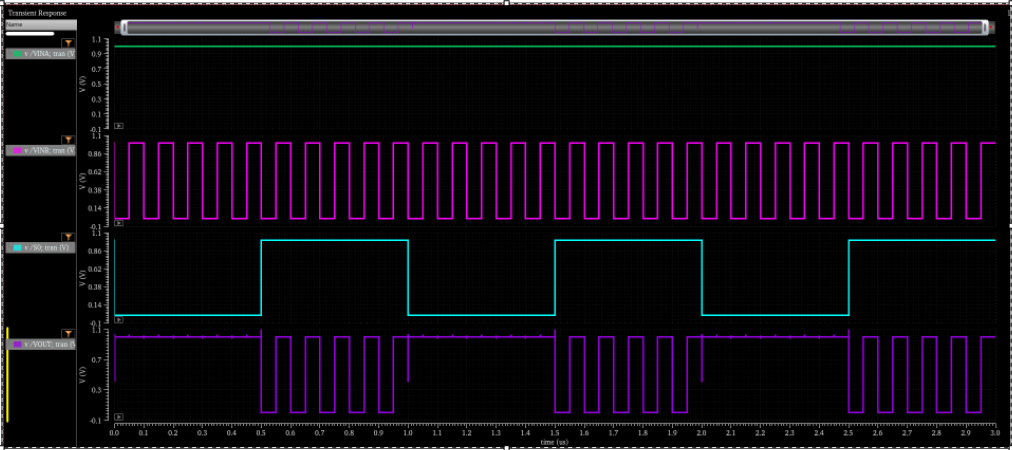

Test

Simulation

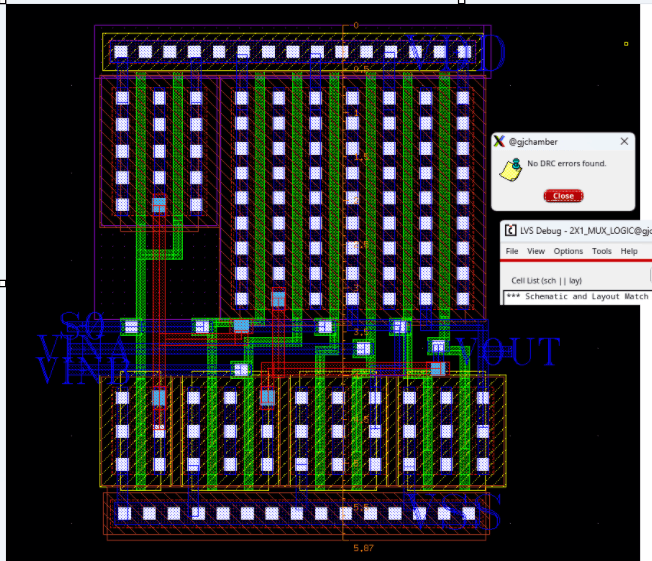

Layout

- Schematic에 맞게 NOT 1개, 2NAND 3개를 배치한다.

- NOT이 2NAND보다 길기 때문에 fingers를 2로 바꿔 낭비되는 크기를 줄인다.

- 2NAND의 pMOS는 하나로 바꾼다.

- 이후 Schematic에 맞게 배선 한다. 이때 Metal이 겹치는 부분이 있으므로 Metal2를 사용한다.

가로 : 4.63u 세로 : 5.87u 크기 : 27.1781

Switch

- S값을 통해 특정 입력을 선택하는 회로이다.

- 이 회로의 조합을 통해 MUX를 만들수 있다.

- Logic Gates 조합을 통한 MUX보다 트랜지스터 갯수를 줄일 수 있다.

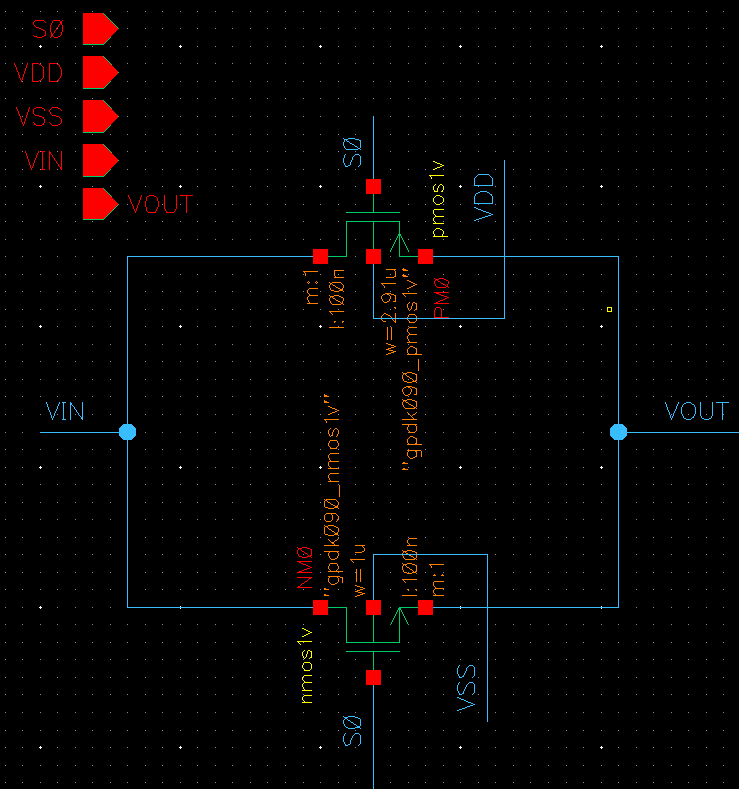

Schematic

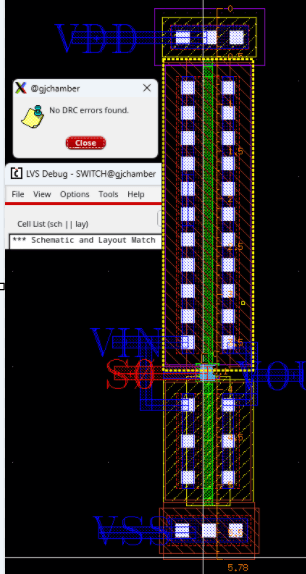

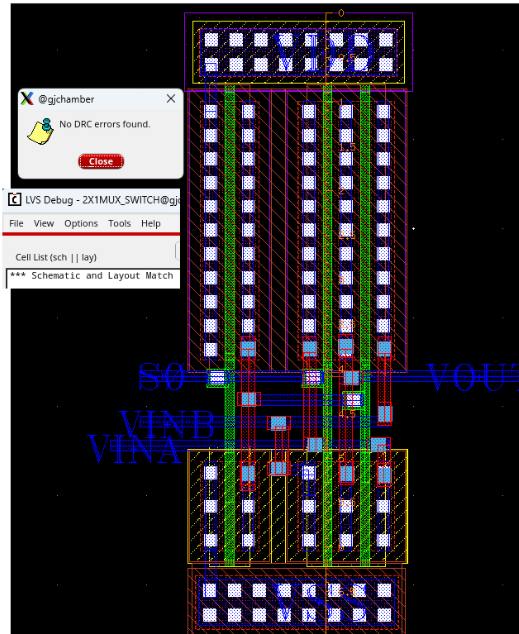

Layout

2X1 MUX SWITCH

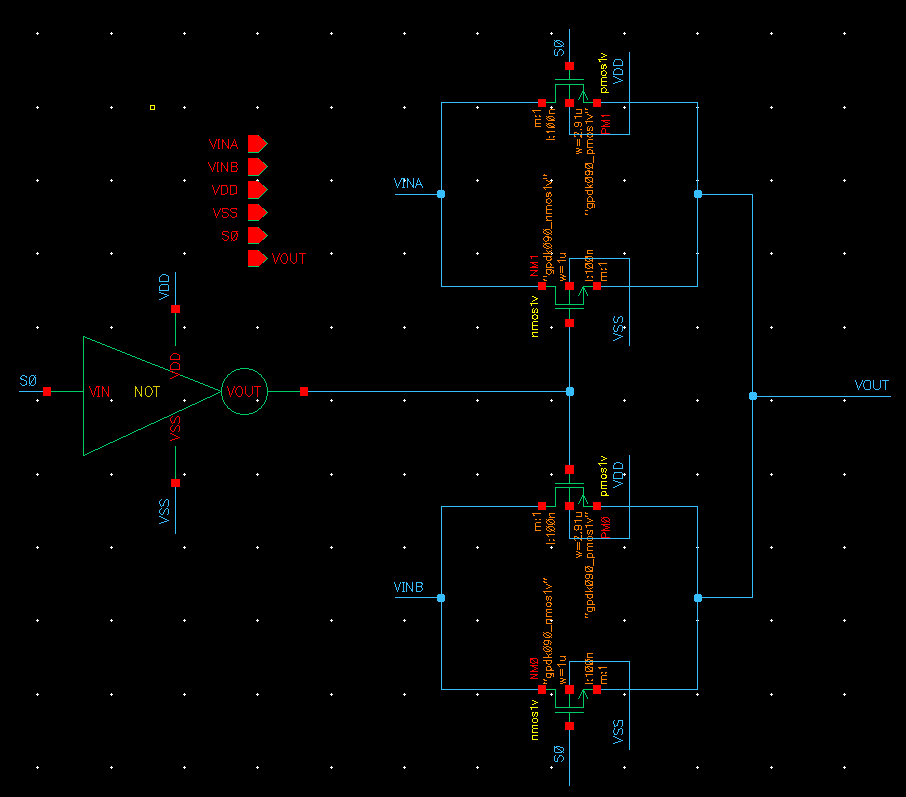

Schematic

- 트랜지스터 수 : 2(SWITCH) X 2 + 2(NOT) = 6개

- Logic gate 들을 사용한 것 보다 8개가 감소했다.

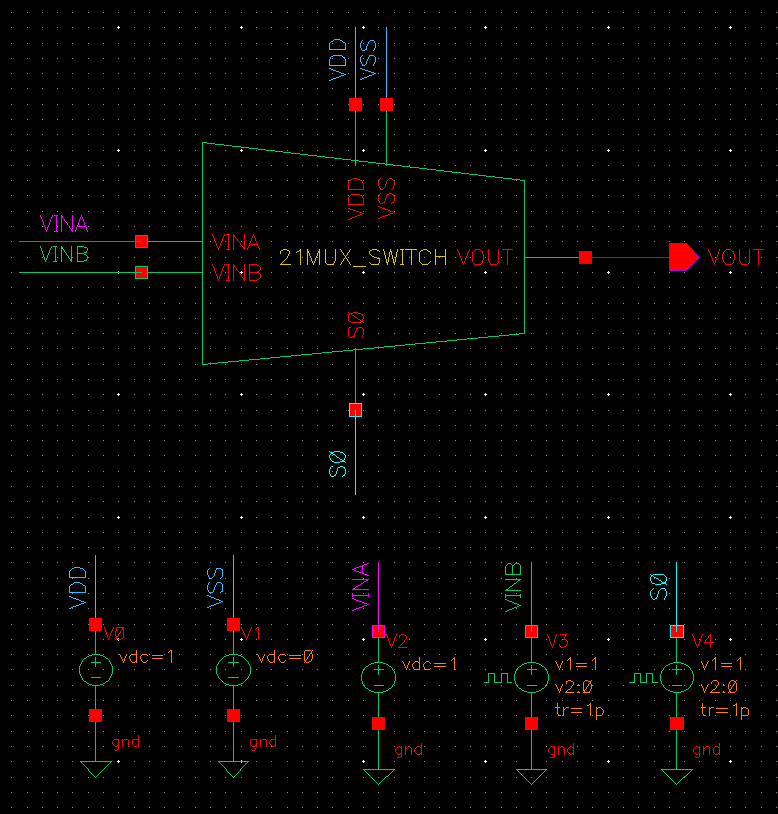

Test

Simulation

Layout

- SWITCH 2개는 동일한 VDD, VSS를 사용하므로 가로 길이를 줄이기 위해 FINGERS를 2로하여 수정한다.

- VDD, VSS는 가능한 크게 하는 것이 소자 수명에 유리하다. 이를 고려해서 VDD, VSS는 2Colums로 적용했다.

- 가로는 Metal1, 세로는 Metal2를 사용해 Layout을 그린다.

가로 : 2.47u 세로 7.06u 전체 : 17.4382

'ARM 코어 기반 반도체 설계 제어 전문가 과정 > CUSTOM IC ONE CHIP' 카테고리의 다른 글

| [CUSTOM IC ONE CHIP] 8X1 MUX - Logic OR Switch (16) (0) | 2025.04.30 |

|---|---|

| [CUSTOM IC ONE CHIP] 4X1 MUX - Logic OR Switch (15) (0) | 2025.04.28 |

| [CUSTOM IC ONE CHIP] Layout-2 (13) (0) | 2025.04.18 |

| [CUSTOM IC ONE CHIP] Layout (12) (0) | 2025.04.17 |

| [CUSTOM IC ONE CHIP] CMOS Schematic (11) (0) | 2025.04.16 |