2025-04-17

에러 검증

- LVS (LAYOUT VS SCHEMATIC) : 작성한 Layout이 Schematic과 일치하는지 검증

- DRC(DESIGN RULE CHECK) : 작성한 Layout이 Design Rule(공정 규칙)을 잘 지켰는지 검증 EX) Metal - Metal : 0.12um, Poly - Oxide : 0.1um 등

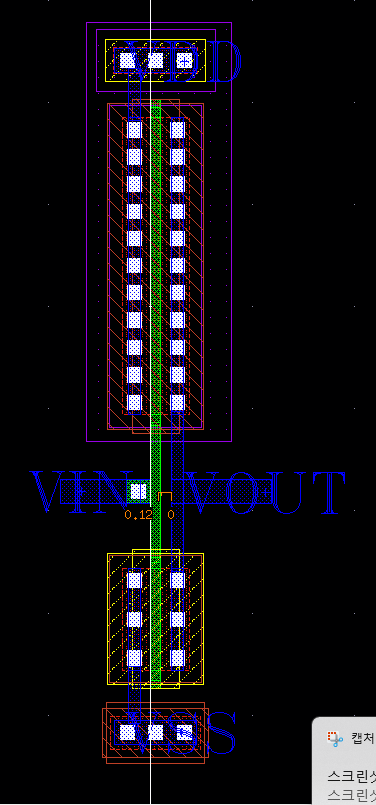

CMOS NOT

Schematic & Layout

- 현재 pMOS는 Nwell이 존재하고 nMOS는 소스와 드레인에 해당하는 n+층이 존재한다.

- 즉 p substrate는 검은 바탕 전체를 의미한다.

Layout 순서

- 먼저 Schematic에 맞게 p,nMOS를 위 아래로 배치한다.

- Schematic에 맞게 배선 연결을 한다. Contact은 좌측을 소스 우측을 드레인으로 가정한다.

- BODY를 만든다. 실제 BODY는 하단에 존재 하지만 연결을 위해서는 Contact을 통해 같은 높이에 위치하게 한다.

- pMOS는 BODY가 Nwell에 존재하므로 Metal - Nwell Contact을 배치한다. 이 부분을 소스와 연결한다.

- nMOS는 p substrate에 BODY가 존재하므로 Metal - Psub Contact을 배치한다. 이 부분을 드레인과 연결한다.

- VIN도 Contact을 만들어 준다.

- 입 출력 노드에 라벨링을 해준다.

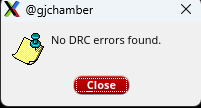

DRC

- Nwell에 관한 에러 발생

- VDD는 pMOS의 BODY와 연결되어 있다. BODY는 Nwell 에서 온것이기 때문에 pMOS의 Nwell과 VDD에 존재하는 Nwell은 연결되어 있어야 한다.

- 이를 해결하기 위해 pMOS와 VDD를 한 Nwell 로 감싼다. 같은 레이어는 가장 외각선만 고려한다.

LVS

Layout 최소화

- 반도체의 비용은 크기에 반비례하기 때문에 DRC, LVS를 만족하는 최소 크기로 Layout을 그려야 한다.

CMOS 2NAND

Schematic & Layout

Layout 순서

- NOT과 동일하게 n, pMOS를 불러온다. 이때 입력이 2개 이므로 속성에서 Fingers를 2로 바꿔준다.

- 2 입력 중 A, B를 선택한다. 여기서는 오른쪽을 A로 선택한다.

- Schematic에 맞게 INPUT, VDD, VSS, VOUT을 배선한다.

- pMOS의 body와 pMOS를 Nwell로 감싸준다.

- 입력에 Cont를 추가하고 입출력을 라벨링한다.

DRC & LVS

Layout 최소화

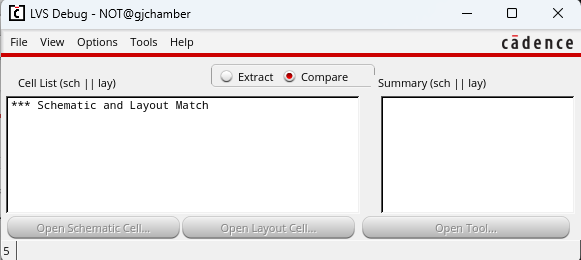

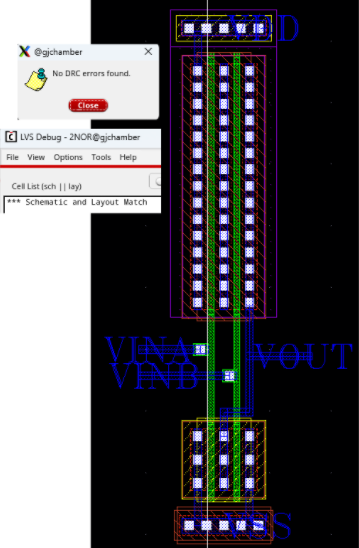

CMOS 2NOR

Schematic & Layout

Layout 순서

- 2NAND와 동일하게 n,pMOS의 Finger을 2로 변경한다.

- VOUT을 핀을 줄이기 위해 왼쪽을 A, 오른쪽을 B로 정한다.

- Schematic에 맞게 INPUT, VDD, VSS, VOUT을 배선한다.

- pMOS의 body와 pMOS를 Nwell로 감싸준다.

- 입력에 Cont를 추가하고 입출력을 라벨링한다.

DRC & LVS

Layout 최소화

728x90

'ARM 코어 기반 반도체 설계 제어 전문가 과정 > CUSTOM IC ONE CHIP' 카테고리의 다른 글

| [CUSTOM IC ONE CHIP] 2X1 MUX - Logic OR Switch (14) (0) | 2025.04.28 |

|---|---|

| [CUSTOM IC ONE CHIP] Layout-2 (13) (0) | 2025.04.18 |

| [CUSTOM IC ONE CHIP] CMOS Schematic (11) (0) | 2025.04.16 |

| [CUSTOM IC ONE CHIP] Channel Length Modulation (10) (0) | 2025.04.14 |

| [CUSTOM IC ONE CHIP] Body Effect (09) (0) | 2025.04.14 |