2025-04-11

VIRTUOSO

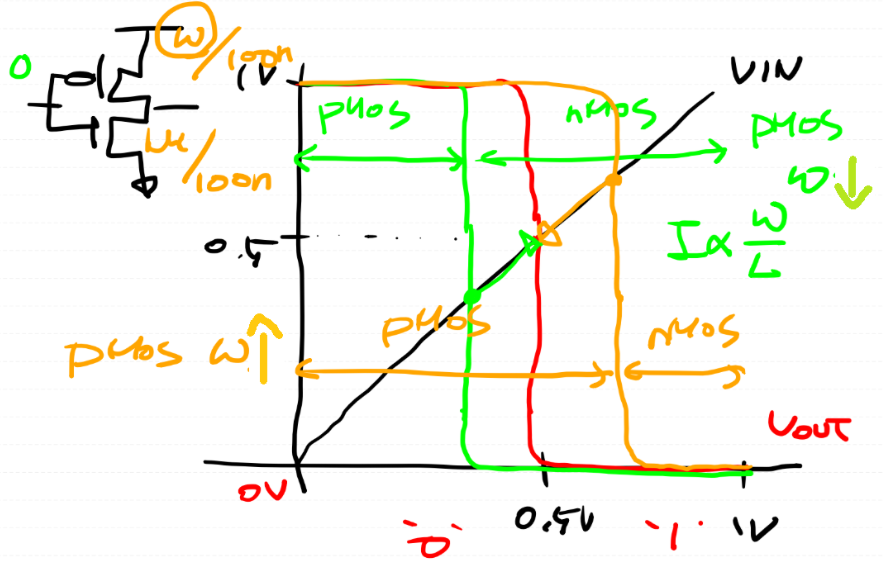

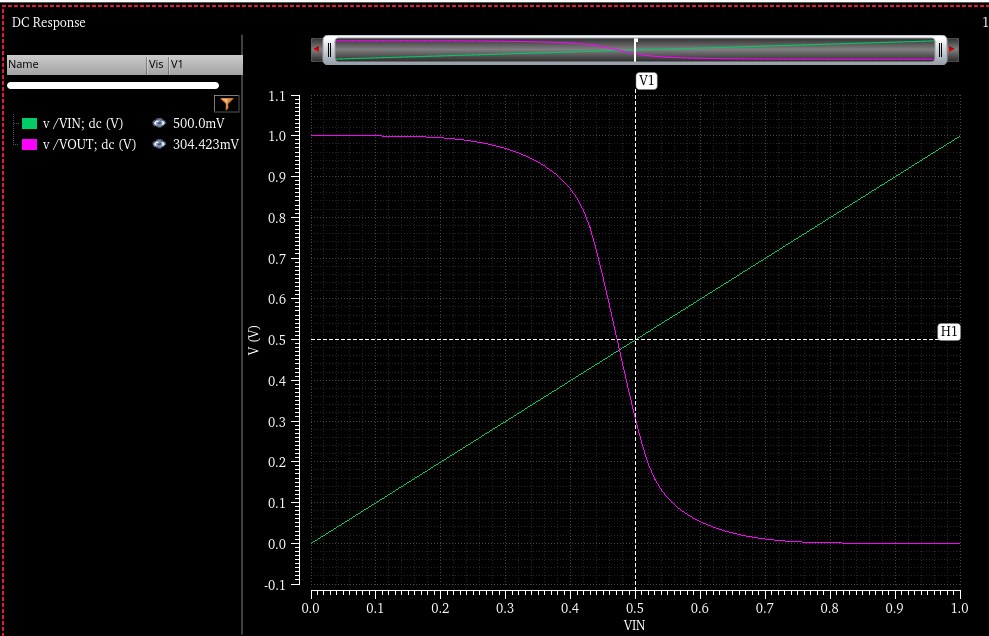

Inverter 출력 파형 해석

- 입력이 0일 경우 pMOS, 1인 경우 nMOS가 ON 된다.

- 이 때문에 출력이 변하는 순간의 좌측 구간이 pMOS, 우측이 nMOS 구간이 된다.

- 정상 작동을 위해서는 두 구간의 범위가 같아야 한다.

- nMOS의 W를 고정 시켰을 때 pMOS의 W가 증가하면 pMOS 영역이 증가하고 감소하면 nMOS 영역이 증가한다.

NAND, NOR Simulator

|

AB

|

NAND

|

NOR

|

|

00

|

1

|

1

|

|

01

|

1

|

0

|

|

10

|

1

|

0

|

|

11

|

0

|

0

|

- NAND는 A는 1로 고정 시키고 B를 변화 시켜 출력 파형을 관찰한다.

- NOR은 A는 0으로 고정 시키고 B를 변화 시켜 출력 파형을 관찰한다.

CMOS Inverter

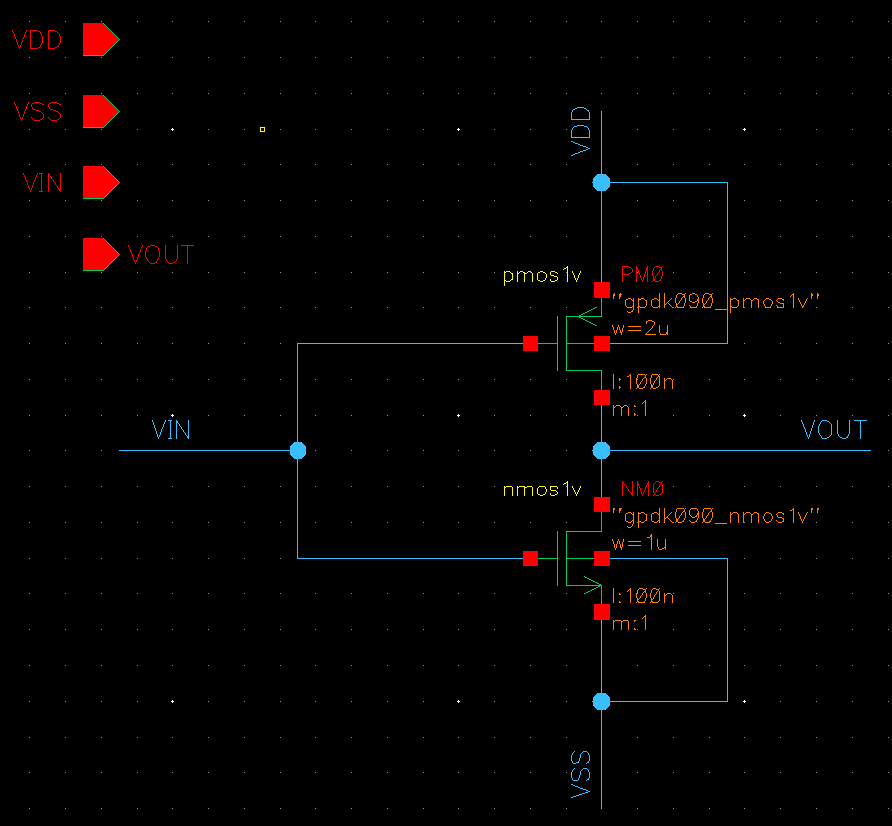

Schematic

- (pMOS width : 2u, nMOS width : 1u)

- Hole의 이동도가 Electron의 이동도 보다 느리기 때문에 동일 전류를 위해서는 크기 차이가 필요하다.

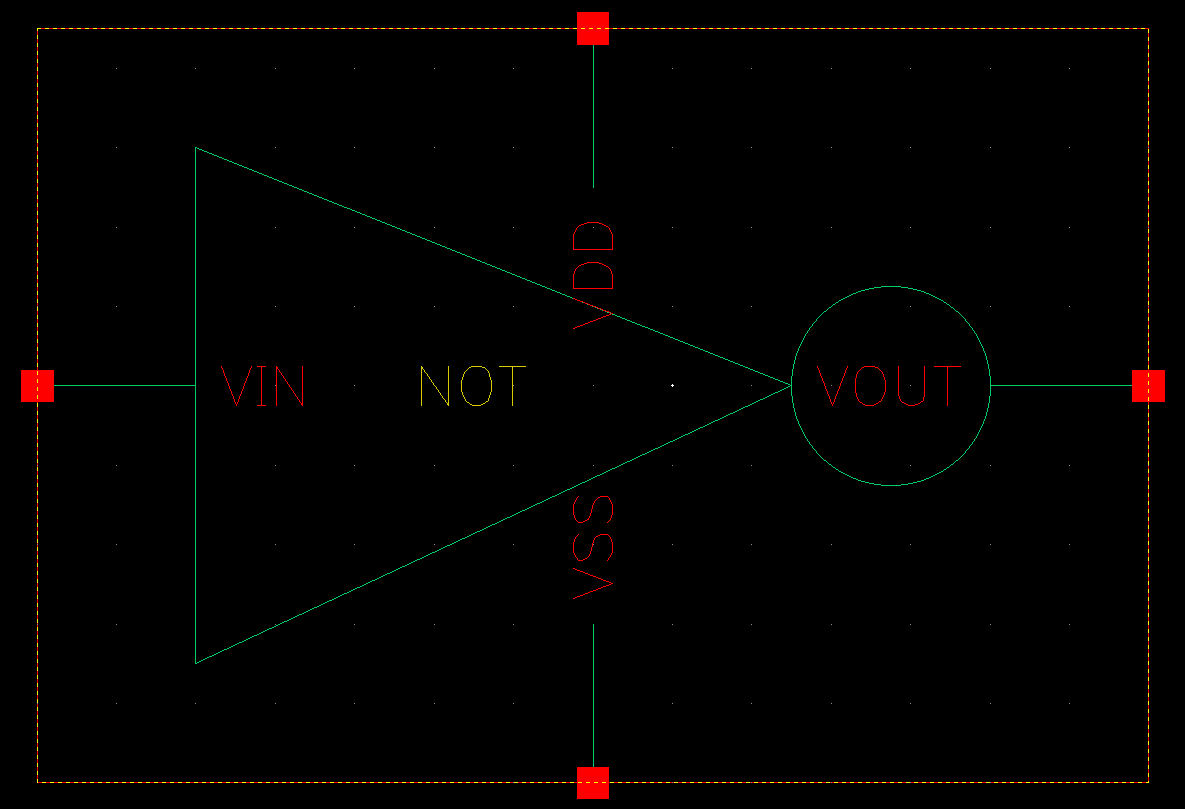

Symbol

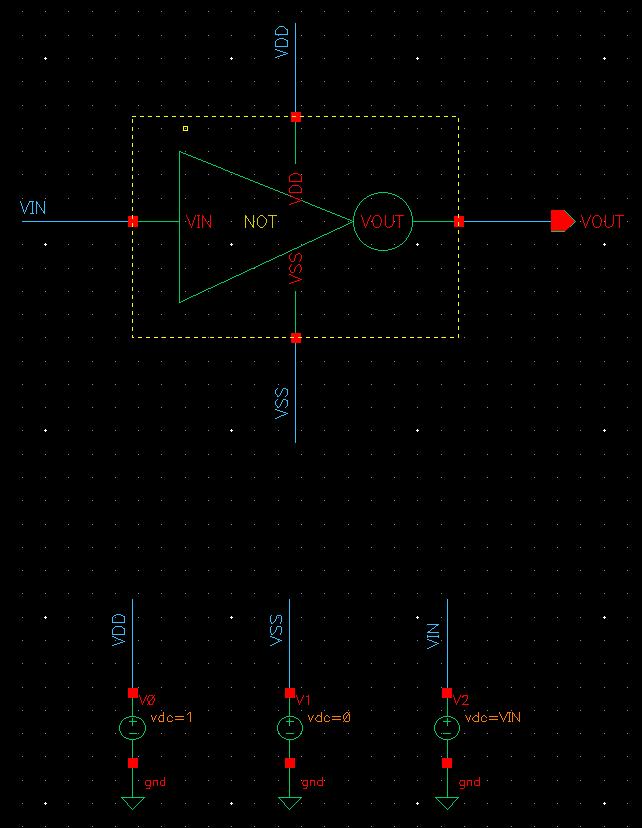

Test Schematic

Simulation

- Inverter가 정상 작동하려면 Vout 파형이 (0.5,0.5) 지점과 만나야 한다.

- 즉 파라미터 기능을 통해 pMOS의 Width 값을 찾아야한다.

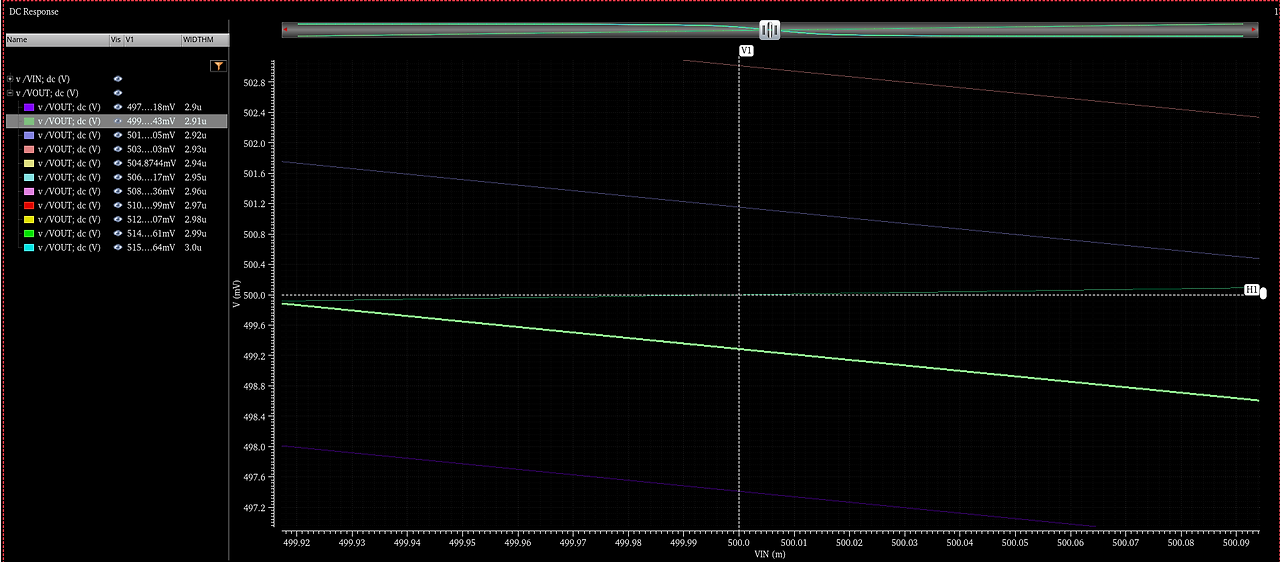

Parameter

- Parameter를 통해 찾은 pMOS Width : 2.91u

- 정확히 (0.5,0.5)와 일치하는 지점을 찾을 수 없기 때문에 소수점 2자리 까지만 찾는다.

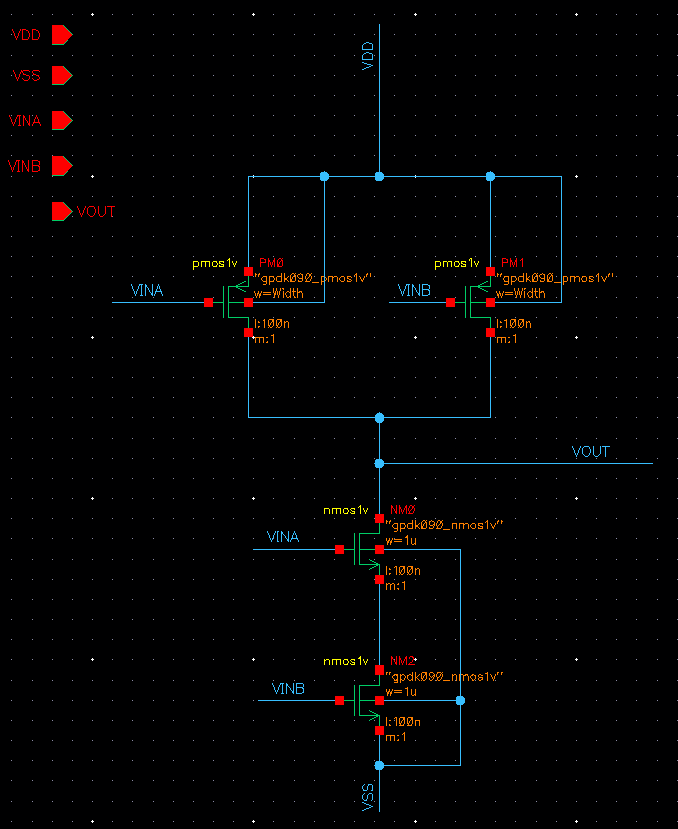

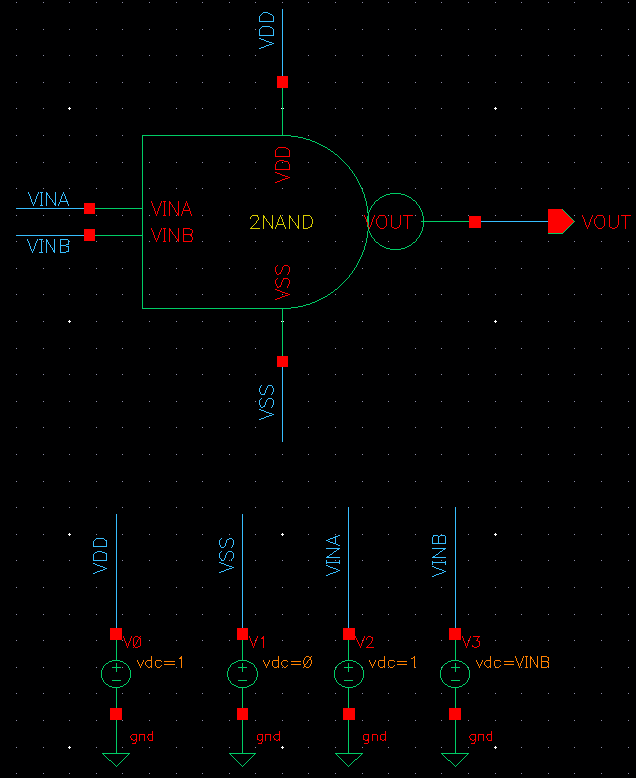

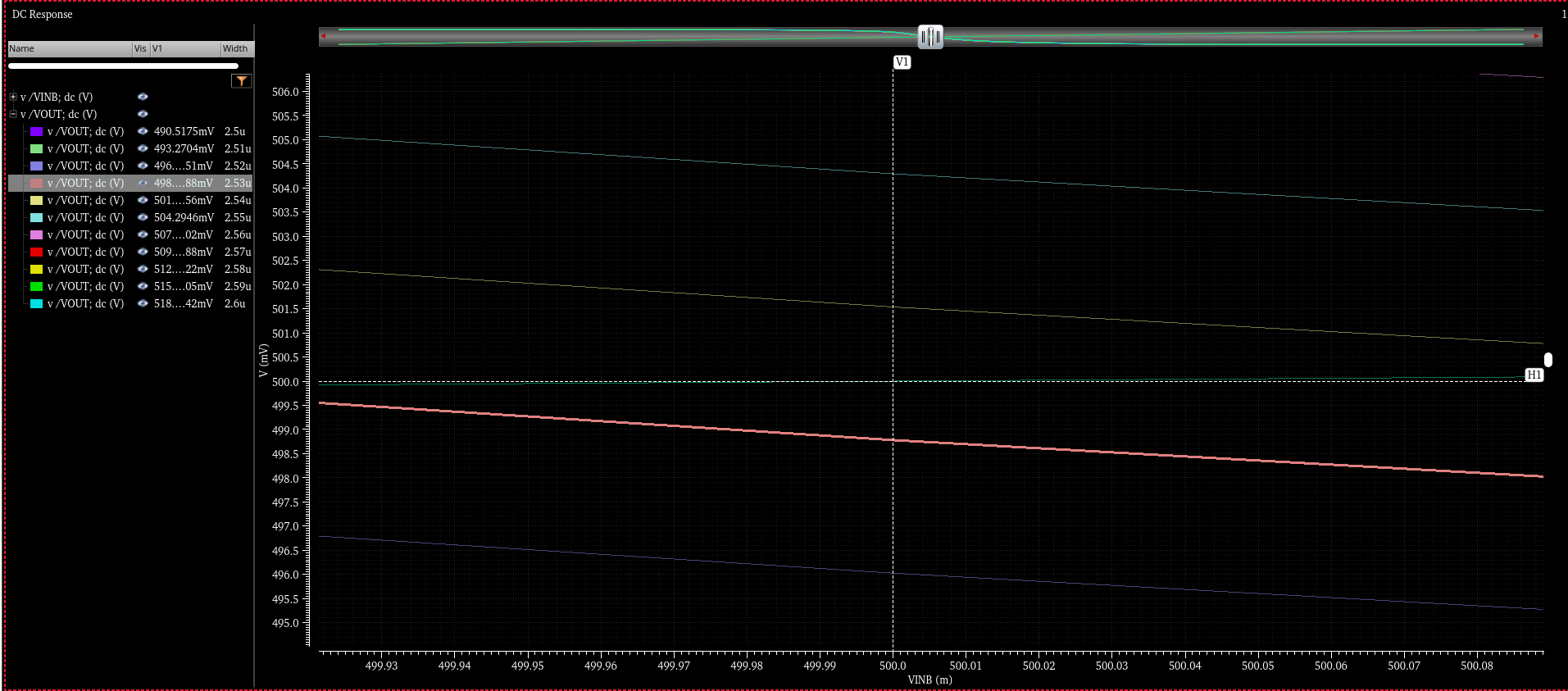

2NAND

Schematic

- pMOS의 적정 Width값을 구하기 위해 w 값은 Width로 두고 parameter 기능을 사용

Symbol

Test Schematic

Parameter Simulation

- (0.5,0.5)와 가장 가까운 지점의 W : 2.53u

'ARM 코어 기반 반도체 설계 제어 전문가 과정 > CUSTOM IC ONE CHIP' 카테고리의 다른 글

| [CUSTOM IC ONE CHIP] MOS Capicator (07) (0) | 2025.04.14 |

|---|---|

| [CUSTOM IC ONE CHIP] NAND .VS NOR (06) (0) | 2025.04.14 |

| [CUSTOM IC ONE CHIP] Stick Diagram Examples (04) (0) | 2025.04.11 |

| [CUSTOM IC ONE CHIP] Stick Diagram (03) (0) | 2025.04.11 |

| [CUSTOM IC ONE CHIP] Inverter Cross-section (02) (0) | 2025.04.11 |