2025-04-10

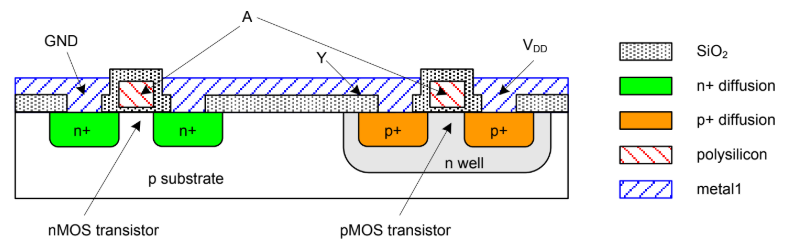

Inverter Cross-section

- p,nMOS의 소스와 바디는 단락되어 있어야 한다.

- 이를 위해 고도핑한 바디 영역을 소스옆에 배치한다.

- 이를 메탈로 연결해 단락시킴이콘 추가한다.

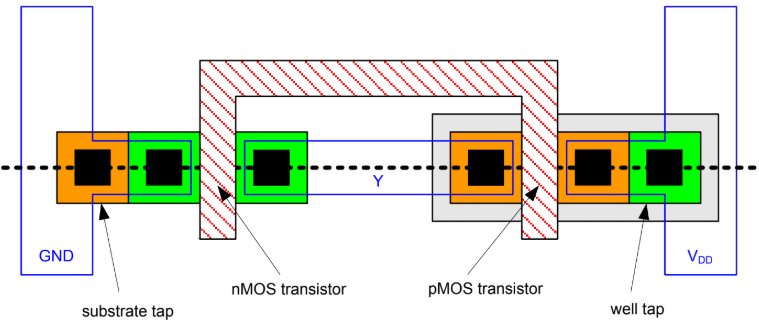

Inverter Mask Set

- Inverter Cross-section을 위에서 바라본 모습으로 공정을 위한 설계도

- 실제로는 HOLE과 ELECTRON의 속도 차이 존재한다.

- 즉 nMOS와 pMOS를 동일한 크기로 만들면 전류량이 달라진다.

- 이로 인해 정상 작동이 불가하므로 수정이 필요하다.

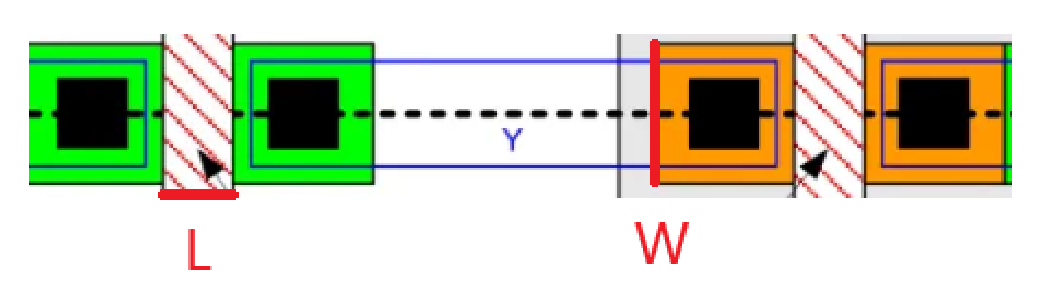

- ELECTRON속도가 2배 빠르다 가정했을때 pMOS의 L을 2배 줄이거나 W를 2배 키워 그려야 한다.

- 전류는 채널 길이인 L에 반비례하고 MOS의 넓이인 W에 비례한다.

Layout

- 칩의 mask를 그리는 작업

- Feature size f = distance between source and drain

- ex) λ=0.3μm in 0.6μm process

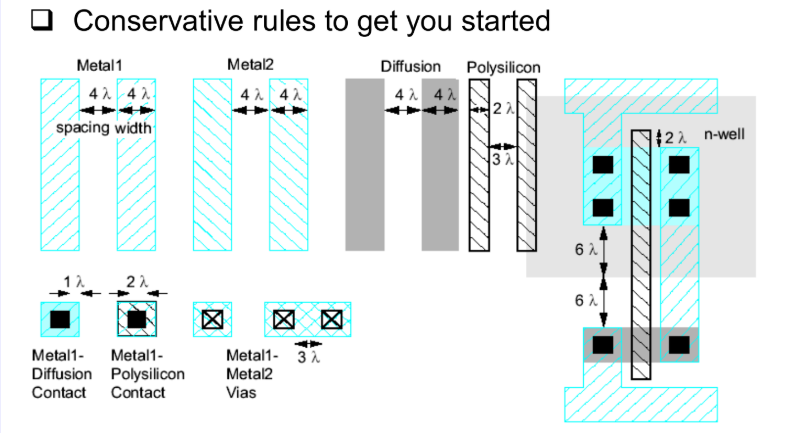

Design Rules

- fab마다 사용하는 Design Rule

- 위의 Design Rule을 토대로 레이아웃을 만들어야 한다.

'ARM 코어 기반 반도체 설계 제어 전문가 과정 > CUSTOM IC ONE CHIP' 카테고리의 다른 글

| [CUSTOM IC ONE CHIP] NAND .VS NOR (06) (0) | 2025.04.14 |

|---|---|

| [CUSTOM IC ONE CHIP] NAND,INVERTER (05) (0) | 2025.04.14 |

| [CUSTOM IC ONE CHIP] Stick Diagram Examples (04) (0) | 2025.04.11 |

| [CUSTOM IC ONE CHIP] Stick Diagram (03) (0) | 2025.04.11 |

| [CUSTOM IC ONE CHIP] CMOS Schematic (01) (0) | 2025.04.11 |