2025-04-09

IC (Integrated circuits)

- 집적 회로 : 한 칩에 많은 트랜지스터가 집적되어 있는 회로

VLSI (Very Large Scale Integration)

|

구분

|

풀네임

|

특징

|

|

SSI

|

Small

|

게이트 수준 논리회로

|

|

MSI

|

Medium

|

MUX, Decoder, Counter 등의 조합회로

|

|

LSI

|

Large

|

간단한 CPU, 메모리 등

|

|

VLSI

|

Very Large

|

마이크로프로세서, DSP, RAM 등

|

|

ULSI

|

Ultra Larege

|

복잡한 CPU, GPU, SoC 등

|

- 트랜지스터의 집적도에 따라 분류

CMOS (Complementrary Metal Oxide Semiconductor)

- 직역하면 상보적 MOS

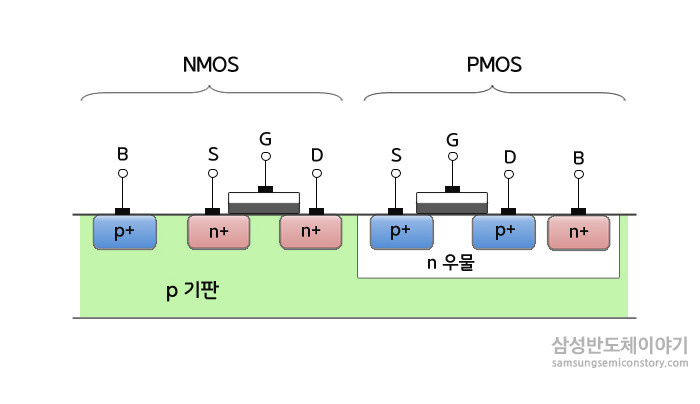

- nMOS + pMOS가 서로 한 쌍을 이루어 존재

- 서로 보완적으로 동작하기에 Complementary가 붙어 CMOS라 불림

특징

Low Power

- nMOS와 pMOS가 동시에 켜지지 않기에 Vdd와 Gnd 직접 연결이 없음

- 이로 인한 전류가 발생하지 않음

- 결국 스위칭을 제외하고는 전력 소모가 매우 적게 발생

Cheap

- 수직 수평 배치 가능으로 인한 효율적 공간 사용

- 2개의 트랜지스터를 통해 여러 논리 게이트 형성 가능

- 저전력 덕분에 열 발생이 줄어 더 높은 집적 가

Fast

- 고집적으로 인해 배선 길이가 짧음

- 전류가 아닌 전압 제어 이므로 신호 지연이 적음

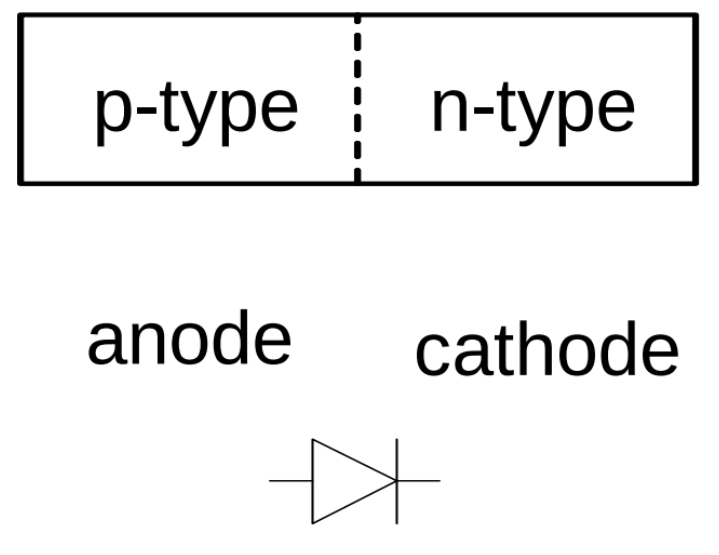

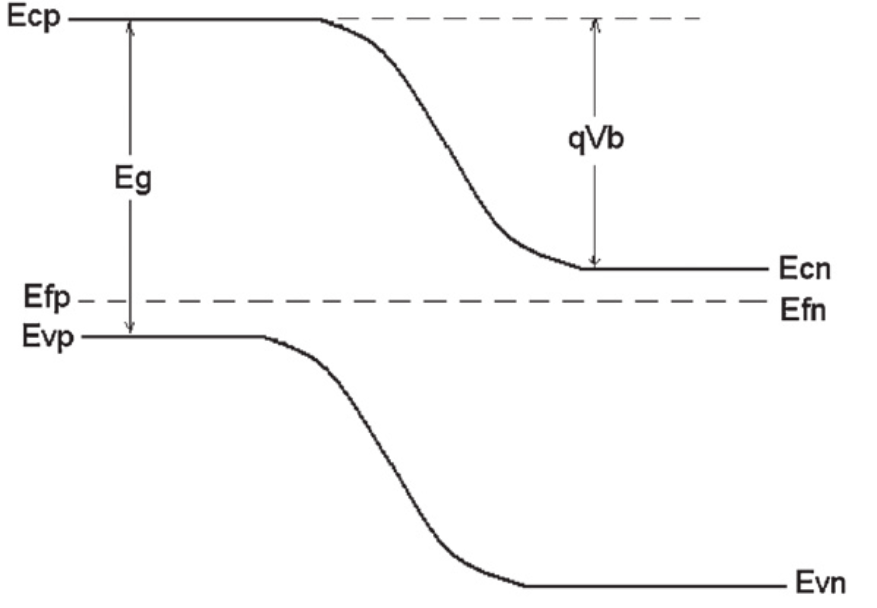

p-n junctions

- 위를 다이오드라 부르며 p를 anode, n을 cathode라 부름

- 다수 캐리어가 hole인 반도체를 p-type

- 다수 캐리어가 electron인 반도체를 n-type

- p-type의 Ef(페르미 레벨)은 Ev(밸런스 밴드)와 가깝게 n-type의 Ef(페르미 레벨)은 Ec(컨덕션 밴드)와 가깝게 존재

- 두 반도체를 접합 시키면 Ef는 고정된 값이므로 각각 Ev, Ec가 변화에 위와 같은 전위 장벽을 형성

- 이때 p-type에 +, n-type에 - 전압을 인가하면 전위 장벽이 감소해 캐리어의 이동이 생기고 전류가 흐름

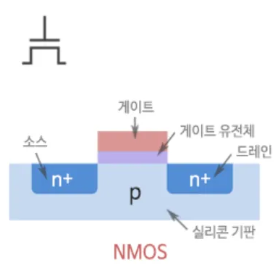

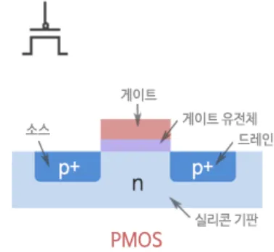

- 게이트, 소스, 드레인, 바디(실리콘 기판) 4단자망 소자

- 게이트 전압에 의해 소스와 드레인 사이에 채널 형성

- 채널을 형성하는 캐리어 종류에 따라 pMOS, nMOS로 구분

FET (Field Effect Transistor)

- 전계 효과 트랜지스터

- G - B, D - S 사이에 각각 수직, 수평 전계 형성

- 이로 인해 채널이 형성되기 때문에 FET란 명칭을 붙임

nMOS

- 게이트, 드레인에는 +전압 소스, 바디에는 -전압 인가

- 이때 바디에 존재하는 전자들이 게이트의 +전압에 의해 모임

- 이로 인해 소스, 드레인 사이에 n채널 형성

- -전압을 사용하지 않기 위해 Gnd로 대체

pMOS

- 게이트, 드레인에는 -전압 소스, 바디에는 +전압 인가

- 이때 바디에 존재하는 정공들이 게이트의 -전압에 의해 모임

- 이로 인해 소스, 드레인 사이에 p채널 형성

- -전압을 사용하지 않기 위해 Gnd로 대체

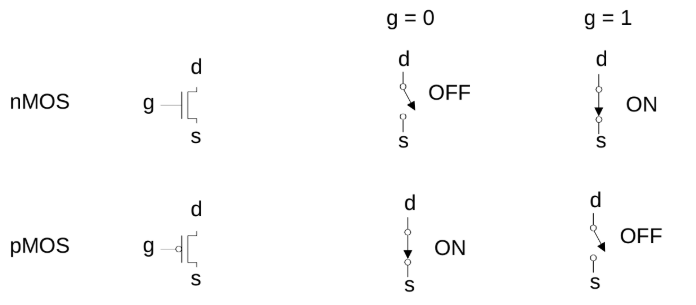

Transistors as Switches

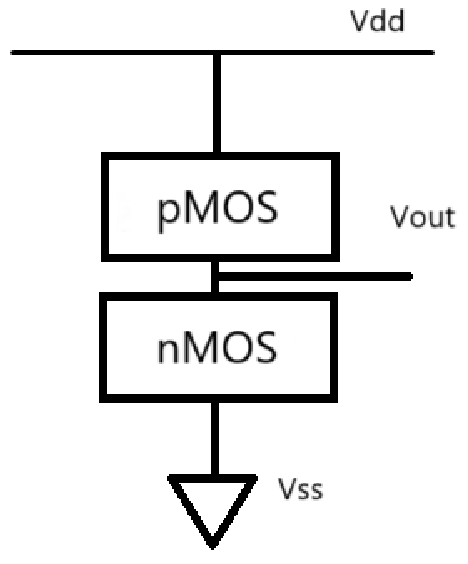

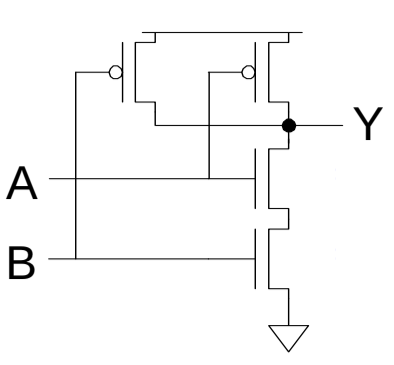

CMOS Schematic

- 위와 같은 형태로 Schematic을 그림

- F = ~X

|

X

|

AND

|

OR

|

|

pMOS

|

병렬

|

직렬

|

|

nMOS

|

직렬

|

병렬

|

- 즉 위는 NAND, NOR을 그리는 방식으로 AND, OR은 각각 F에 인버터를 추가하면 됨

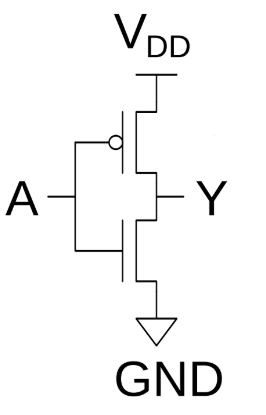

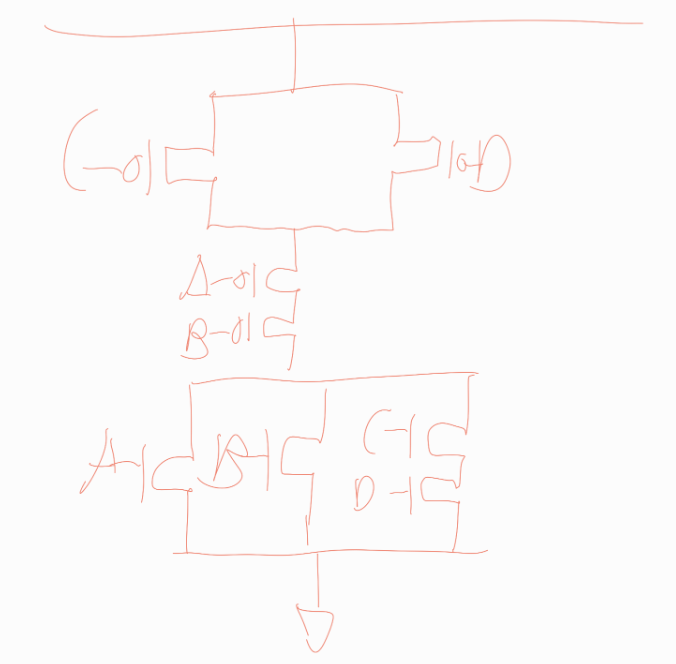

CMOS Inverter

- pMOS의 소스, 바디 nMOS의 드레인, 바디는 단락되어 있음

- 입력당 CMOS 1개로 총 2개의 트랜지스터를 사용

|

|

A

|

스위치

|

Y

|

|

pMOS

|

1

|

OPEN

|

0

|

|

nMOS

|

1

|

CLOSE

|

0

|

|

pMOS

|

0

|

CLOSE

|

1

|

|

nMOS

|

0

|

OPEN

|

1

|

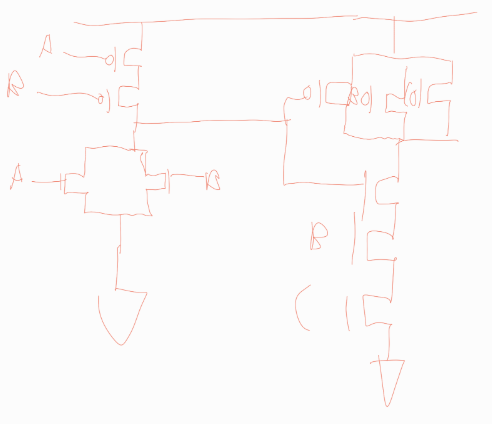

CMOS NAND

- 2 입력이므로 4개의 트랜지스터

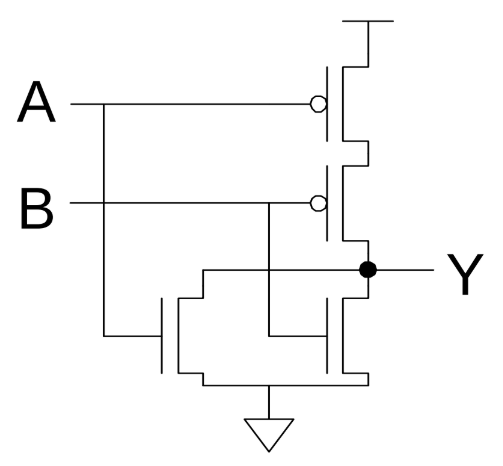

CMOS NOR

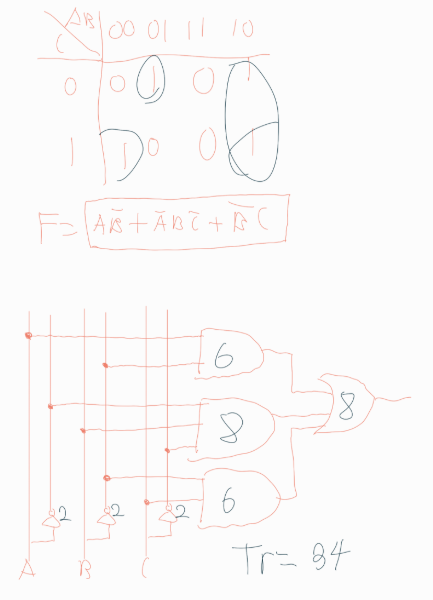

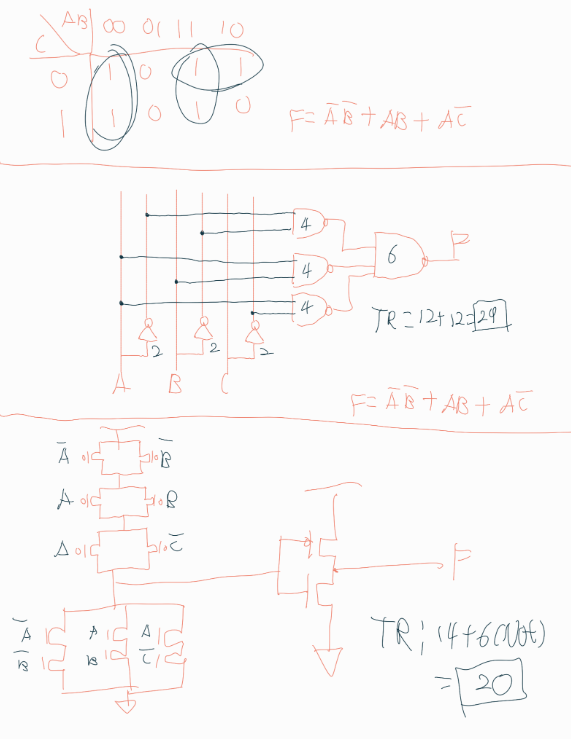

F = ~(A * B + C)

- pMOS와 nMOS 사이가 F이다.

F = ~(A * B + C * D)

F = ~(~(A + B) * B * C)

- pMOS와 nMOS 사이가 F이다.

F = ~(A + B + C * D)

- pMOS와 nMOS 사이가 F이다

F = ~(~(A * B) * (A + B))

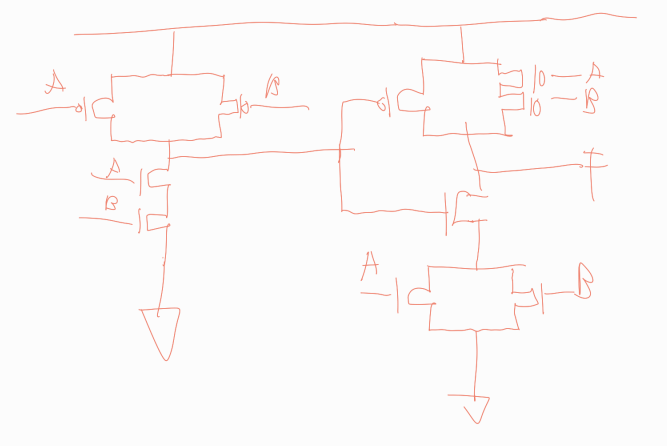

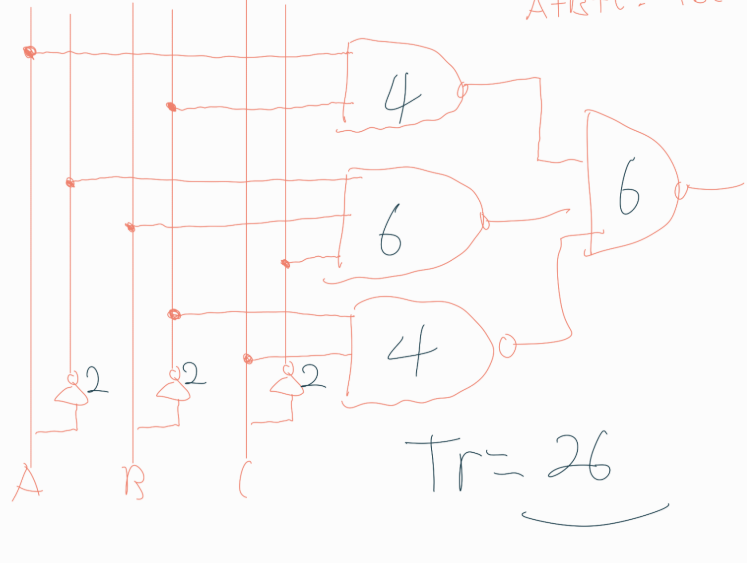

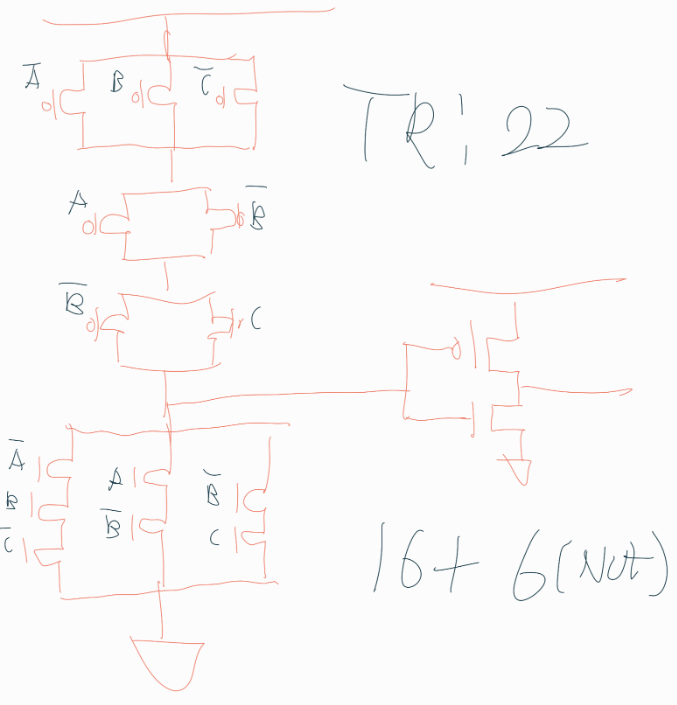

CMOS Schematic .VS Logic Schematic

- 기존 회로상에서 AND의 출력과 OR의 입력에 각각 INV를 추가해 표현 가능

- 이때 드모르간 법칙에 의해 NOT_IN OR은 NAND로 표현 가능

- 이로 인해 트랜지스터 수가 8개 감소한다.

- CMOS Schematic 시 22개로 트랜지스터 수를 더 줄일 수 있음

Transistor를 최소화 해야하는 이유

- 칩의 면적이 줄어들어 비용이 절감됨

- 트랜지스터로 인한 기생 커패시터가 감소함

- 트랜지스터로 인한 전파 지연이 감소함

사진 출처 : 각 사진 클릭시 이동

'ARM 코어 기반 반도체 설계 제어 전문가 과정 > CUSTOM IC ONE CHIP' 카테고리의 다른 글

| [CUSTOM IC ONE CHIP] NAND .VS NOR (06) (0) | 2025.04.14 |

|---|---|

| [CUSTOM IC ONE CHIP] NAND,INVERTER (05) (0) | 2025.04.14 |

| [CUSTOM IC ONE CHIP] Stick Diagram Examples (04) (0) | 2025.04.11 |

| [CUSTOM IC ONE CHIP] Stick Diagram (03) (0) | 2025.04.11 |

| [CUSTOM IC ONE CHIP] Inverter Cross-section (02) (0) | 2025.04.11 |