ARM 코어 기반 반도체 설계 제어 전문가 과정/CUSTOM IC ONE CHIP

[CUSTOM IC ONE CHIP] Project - Scan Chain (01)

whehdud2

2025. 6. 4. 09:59

Scan chain.pptx.pdf

8.47MB

Goals

- 기존 회로를 Scan Chain을 적용

- DFF에 RST 기능을 추가하고, 크기를 최소화

- PASS, FAIL인 경우에 대한 테스트 진행

DFT

'study/DFT' 카테고리의 글 목록

whehdud2 님의 블로그 입니다.

whehdud2.tistory.com

DFT(Scan Cahin)에 대한 이론적 설명은 위 링크에 있습니다.

DFF(NAND OR SWITCH)

NAND

Schematic

- RST신호가 추가된 NAND기반 DFF

- 2NAND 2개, 3NAND 4개, NOT 1개 사용

- NOT은 Active High를 위해 추가함(기본적으로 Active Low로 작동)

Simulation

- RST신호가 High일 때는 OUT(보라색)이 0으로 동작하며 Low일때는 OUT이 IN(초록색) 값으로 나오는 것을 확인

- 이때 CLK(핑크)에 동기화해 OUT이 나온다.

Layout

DRC

LVS

RESE

SWITCH

Schematic

RESET

- SWITCH 4개, 2NAND 2개, NOT 4개 사용

- 우측 하단의 NOT은 Active High를 위해 추가

Simulation

- NAND와 동일하게 작동

Layout

DRC

LVS

NAND VS SWITCH

| TR | Area | |

| NAND | 30 | 67.7 |

| SWITCH | 24 | 63.8075 |

- SWITCH를 사용한 경우가 트랜지스터 수도 적고 크기도 작기 때문에 SWITCH를 사용한 DFF를 이용한다.

Scan FF

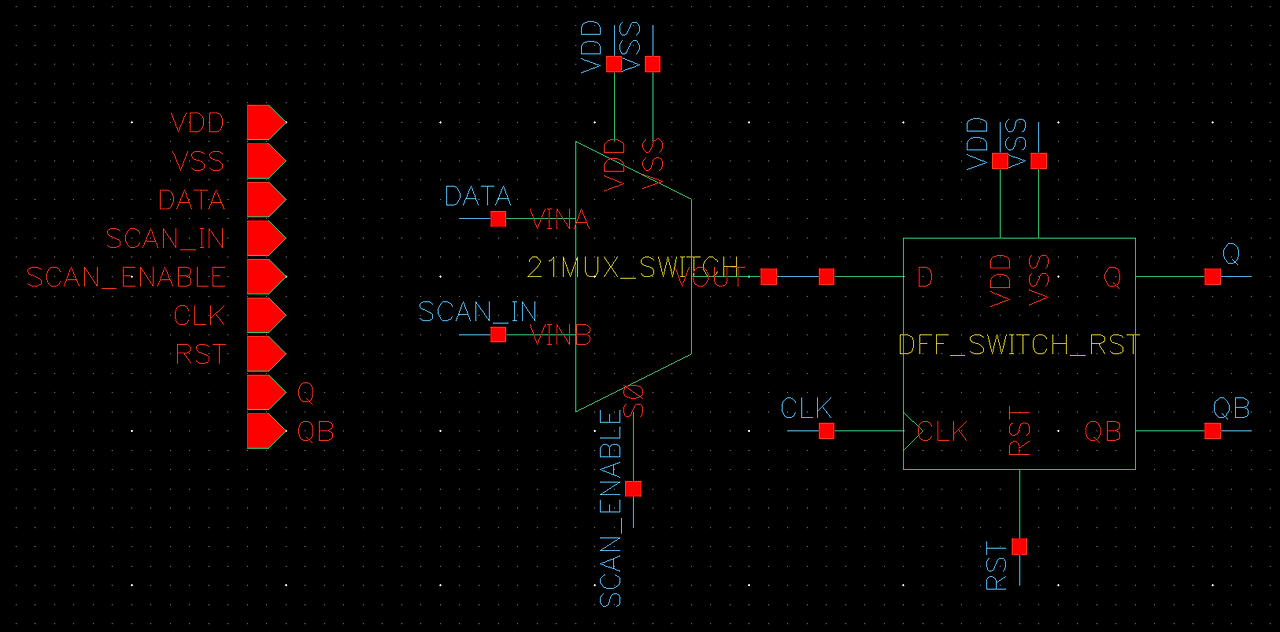

Schematic

- 위에서 설계한 DFF의 입력단에 2X1 MUX를 추가

- SCAN_ENABLE : 테스트 모드와 기능 모드를 제어하는 신호

- SCAN_IN : 테스트 패턴 데이터

- DATA : 기존 데이터

Simulation

- SCAN_EN이 0인 경우 기능 동작, 1인 경우 테스트 동작

- OUT신호가 SCAN_EN이 0일때는 IN값, 1일때는 SCAN_IN으로 나오는 것을 확인

728x90