101 Sequence Detector

- 연속으로 입력되는 특정 입력값을 감지하는 회로

- ex) 1 - 0 - 1이 연속으로 입력될시 OUT은 High

State Diagram

- 현재 상태와 입력에 의해 출력이 결정되는 Mealy Machine으로 설계

- 초기 상태 설정을 위해서 RST신호 추가

- Non overlap 방식 사용 (특정 입력값이 감지된후 초기 상태로 이동)

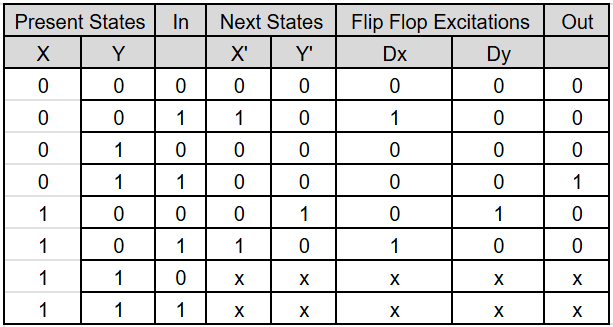

Truth Table

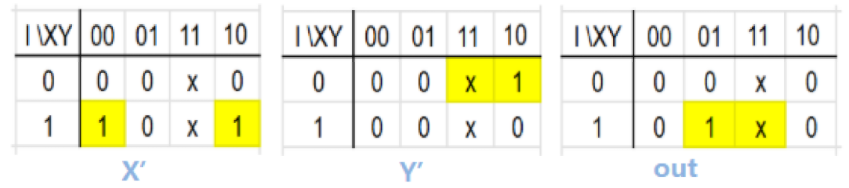

K-map

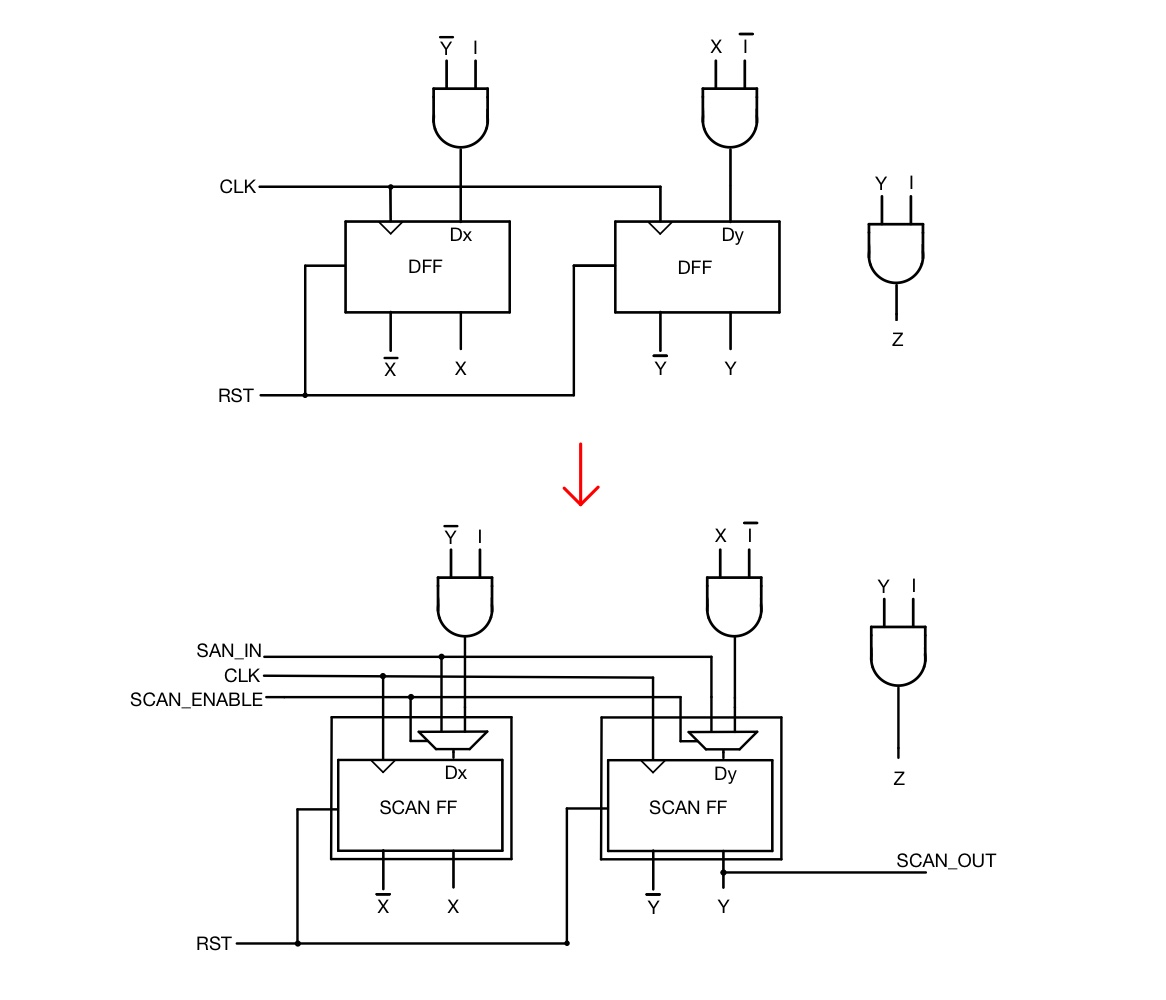

Scan Chain - 101 Sequence Detector

- 상태값은 3개이므로 상태값을 저장하는 DFF는 2개 필요

- DFF를 Scan FF로 교체하여 DFT를 적용한 회로로 수정

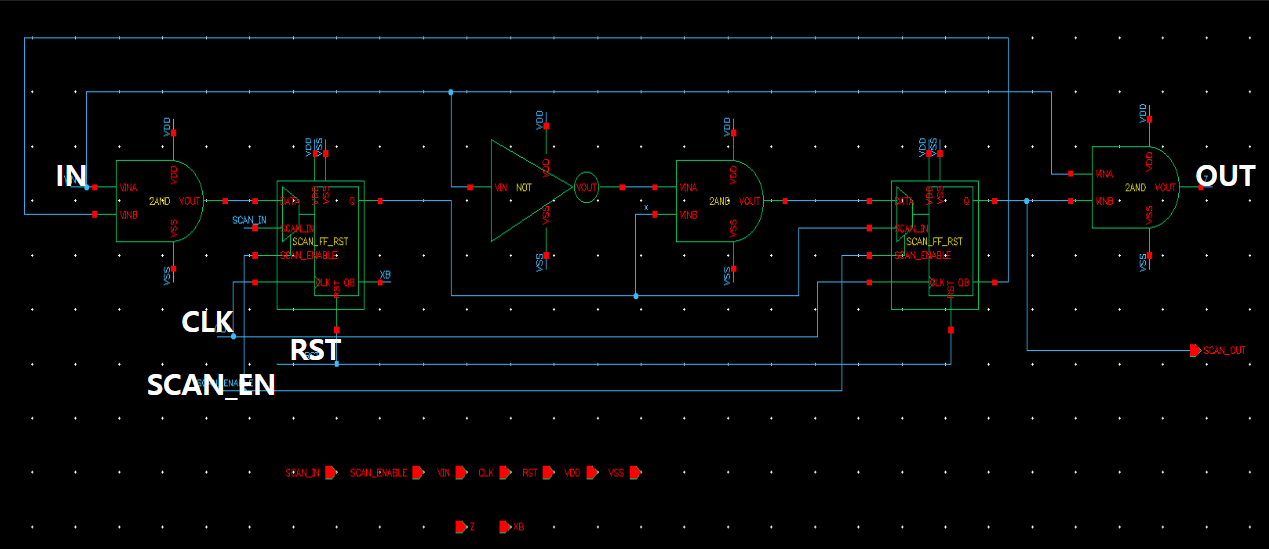

Schematic

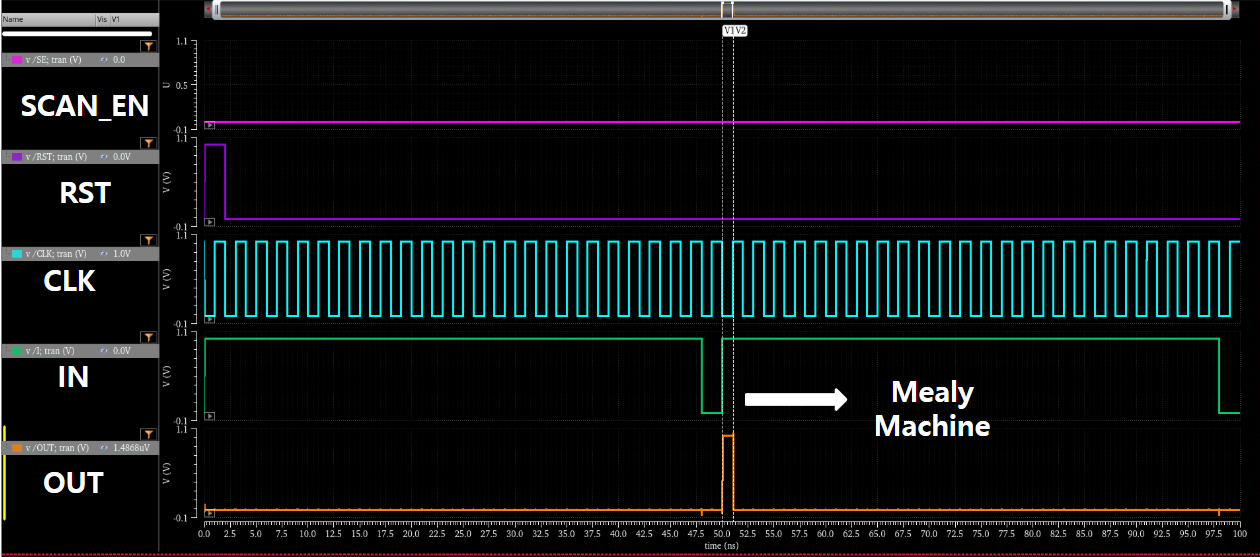

Simulation

기능 동작

- 기능 동작을 위해 SCAN_EN은 0으로 인가

- 초기 상태 정의를 위해 최초 1번은 RST을 High로 인가

- 1 - 0 - 1이 순차적으로 입력될때 출력이 High로 감지됨

- 이때 Mealy Machine이므로 출력값은 CLK에 비동기로 작동

- OUT이 감지된후 다음 CLK에 상태가 초기 상태로 돌아가 출력이 Low로 변화

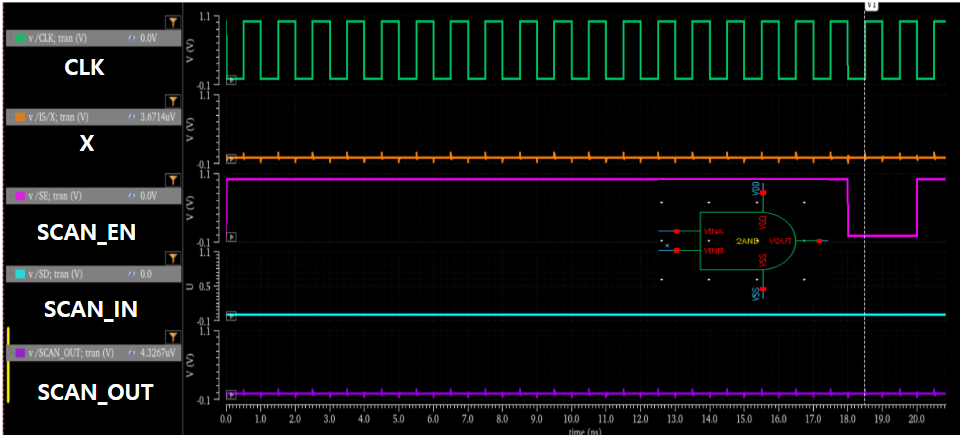

테스트 동작

IN

- AND의 출력값을 테스트

- SCAN_IN으로 0이 입력되었기 때문에 AND의 출력은 항상 0 이여야한다,

- 내부를 스캔한 값인 SCAN_OUT이 CAPTURE가 이뤄진 순간에 0이므로 PASS이다.

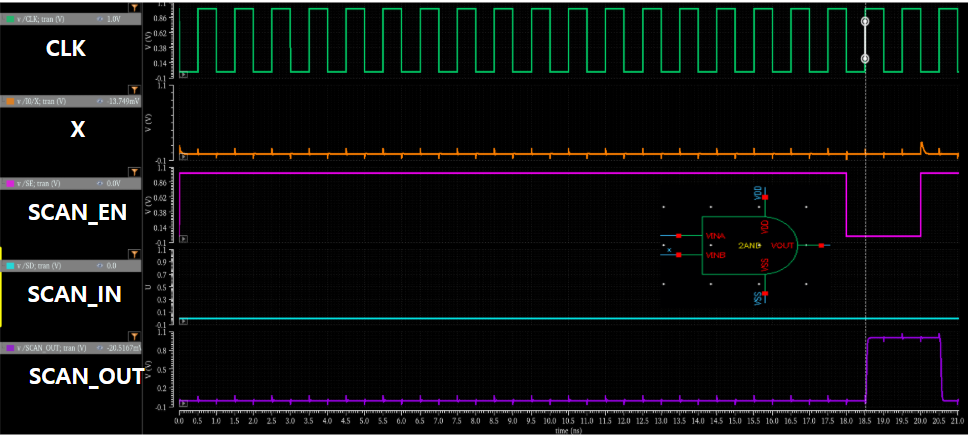

OUT

- AND의 출력에 SA1(Short VDD)이 발생했다 가정

- PASS인 경우와 동일하게 SCAN_IN 입력, 출력은 0이여야한다.

- 내부를 CAPUTRE할때 값이 1이므로 기댓값인 0과 다르다.

- 이 경우는 FAIL

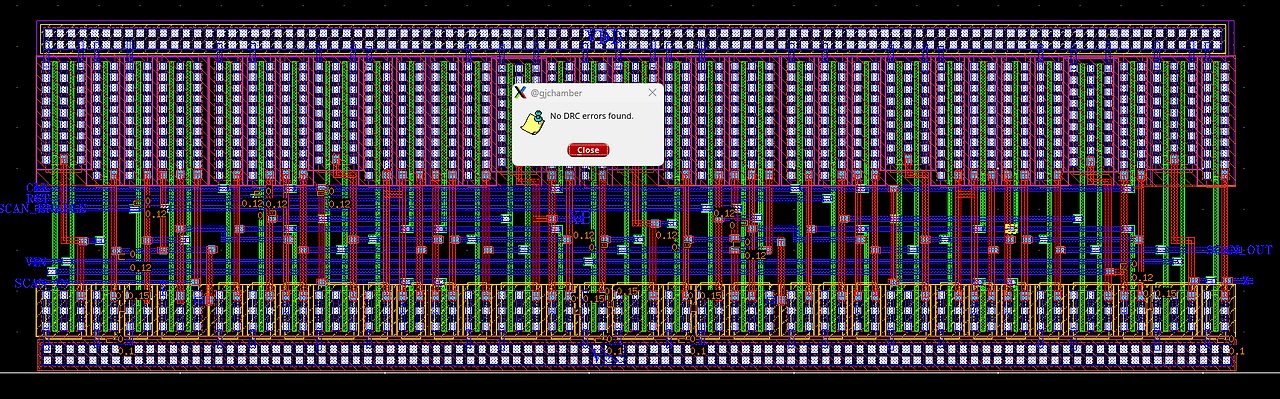

Layout

DRC

CLK

LVS

- Area : 259.8412

RST

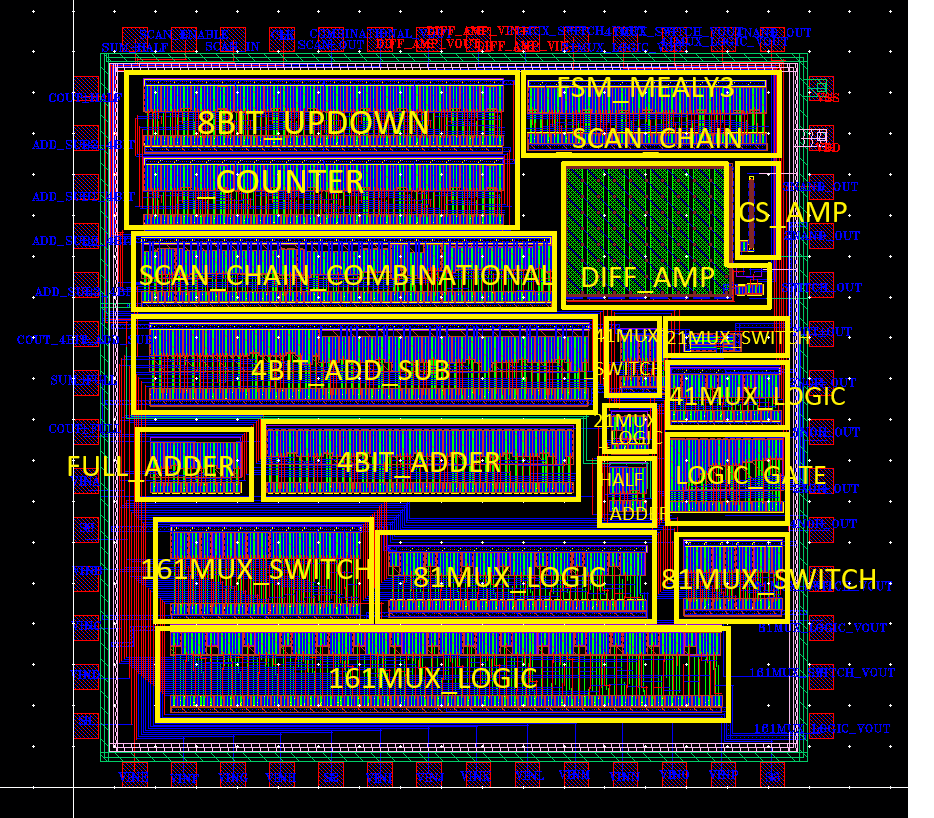

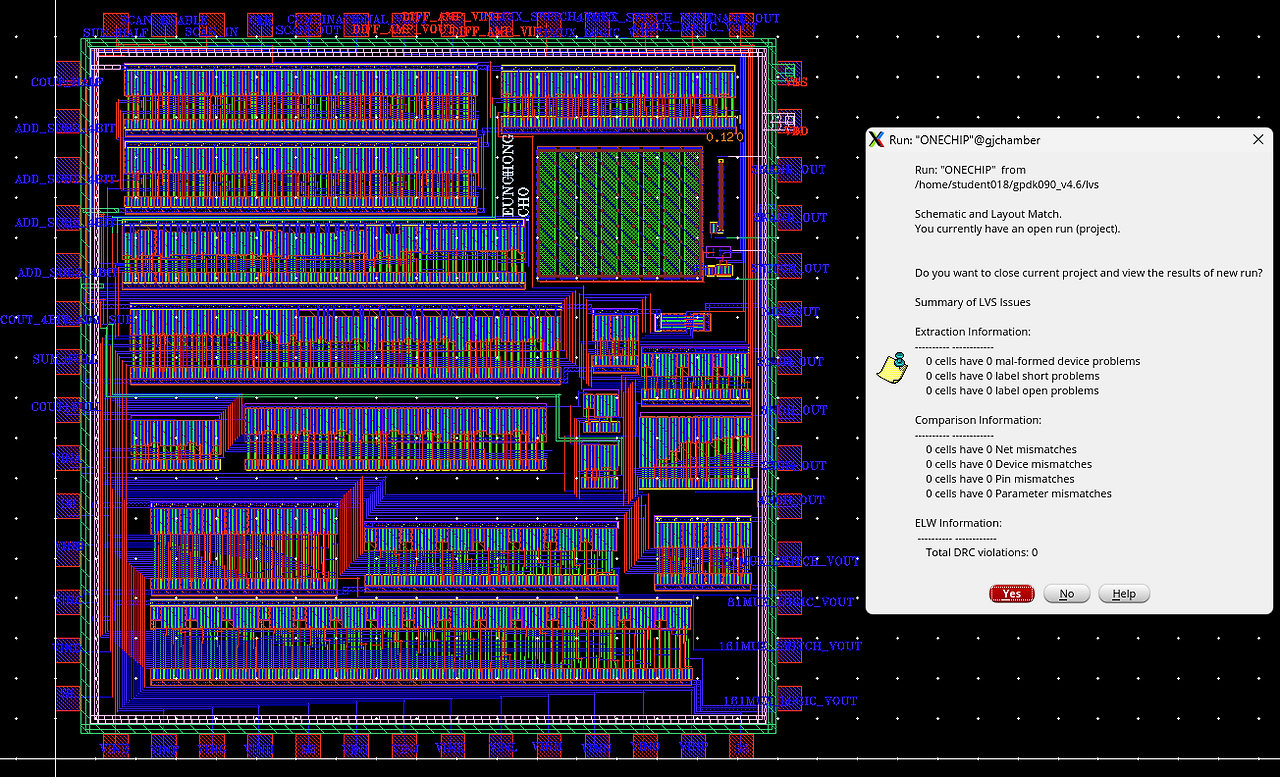

ONE CHIP

Pin Array

SCAN_EN

Parts Array

Layout

DRC

LVS

728x90

'ARM 코어 기반 반도체 설계 제어 전문가 과정 > CUSTOM IC ONE CHIP' 카테고리의 다른 글

| [CUSTOM IC ONE CHIP] Project - Scan Chain (01) (0) | 2025.06.04 |

|---|---|

| [CUSTOM IC ONE CHIP] 4bit ADD/SUB (20) (0) | 2025.05.23 |

| [CUSTOM IC ONE CHIP] ADDER (19) (0) | 2025.05.14 |

| [CUSTOM IC ONE CHIP] XOR (18) (0) | 2025.05.14 |

| [CUSTOM IC ONE CHIP] 16X1 MUX - Logic OR Switch (17) (0) | 2025.05.07 |