study/HDLBits

[HDLBits] Basics (01)

whehdud2

2025. 6. 4. 14:49

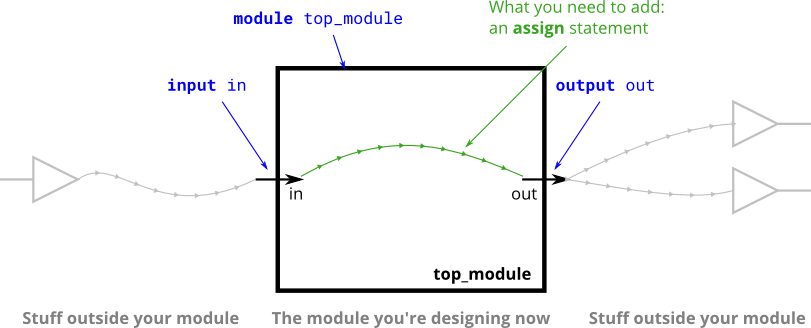

Simple wire

module top_module( input in, output out );

assign out = in;

endmodule4 Wire

module top_module(

input a,b,c,

output w,x,y,z );

assign w = a;

assign x = b;

assign y = b;

assign z = c;

endmodule

NOT gate

module top_module( input in, output out );

assign out = ~in;

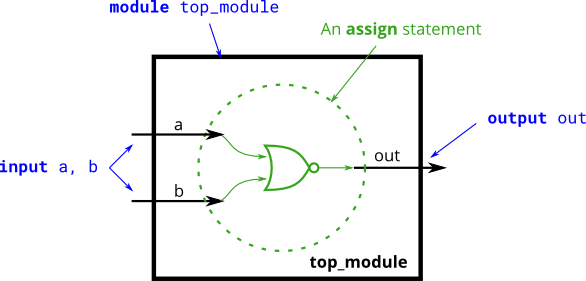

endmoduleAND gate

module top_module(

input a,

input b,

output out );

assign out = a & b;

endmoduleNOR gate

module top_module(

input a,

input b,

output out );

assign out = ~(a | b);

endmodule

XNOR gate

module top_module(

input a,

input b,

output out );

assign out = ~(a ^ b);

endmoduleDeclaring wires

module top_module(

input a,

input b,

input c,

input d,

output out,

output out_n );

wire a_b;

wire c_d;

wire com;

assign a_b = a & b;

assign c_d = c & d;

assign com = a_b | c_d;

assign out = com;

assign out_n = ~com;

endmodule7458 chip

module top_module (

input p1a, p1b, p1c, p1d, p1e, p1f,

output p1y,

input p2a, p2b, p2c, p2d,

output p2y );

wire a_b, c_b, c_d, f_e

;

assign a_b = p2a & p2b;

assign c_b = p1a & p1c & p1b;

assign c_d = p2c & p2d;

assign f_e = p1f & p1e & p1d;

assign p2y = a_b | c_d;

assign p1y = c_b | f_e;

endmodule728x90